#### **COMMUNICATIONS CIRCUITS**

# App Note 3556: Configuring Dallas Semiconductor LIUs Without a Microcontroller

This application note describes how to configure Dallas Semiconductor Line Interface Units (LIUs) without adding the extra, and often complex, circuitry of a microcontroller.

## **Configuration of LIU(s)**

It is possible to configure some Dallas Semiconductor Line Interface Units (LIUs) without a microcontroller. These unique LIUs have an extra serial interface (SPI) along with the traditional parallel port. To place the LIU in SPI slave mode, specific LIU pins are floated, pulled to  $V_{CC}$ , or grounded. Please see the LIU data sheet for particular pin configurations.

Once the LIU is in serial mode, a PROM can be used to provide the LIU with the specific data needed for configuration. If the data in the PROM is formatted in a defined way, the PROM will act like a controller with a SPI interface in Master Mode.

The PROMs typically used for this type of configuration have an internal address accumulator. It is important that the PROMs have this accumulator feature because the PROM will need to automatically jump to the next available address in the configuration memory. We recommend the Xilinx XC18V00 device family which has byte-wide, nonvolatile memory with an autoincrement address function. These devices are available in 1Mb, 2Mb, and 4Mb densities.

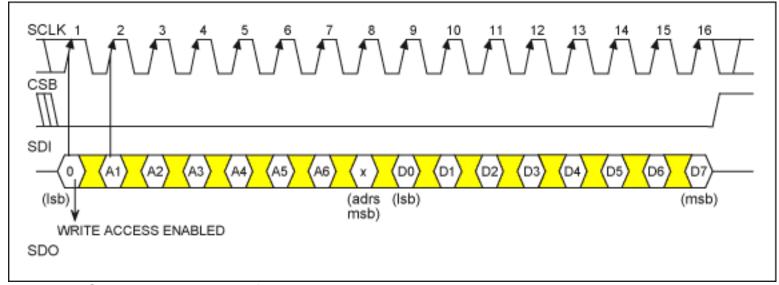

**Figure 1** shows the general relationship of the timing for a SPI bus. For this case, all data is clocked into the slave device on the rising edge of SCLK. This feature can be configurable on some devices; please check the device data sheet for details.

Figure 1. Serial-port operation for write access.

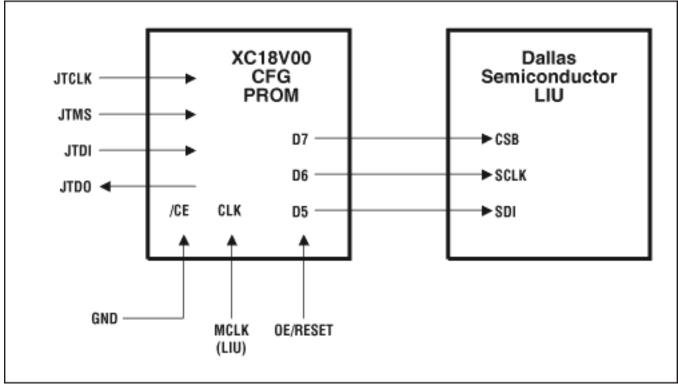

**Figure 2** is a simplified diagram of the Xilinx XC18V00 device and a Dallas Semiconductor LIU in SPI mode. Two key points should be noted.

- The CLK for the Xilinx XC18V00 can be the MCLK for the LIU, but the CLK is not the SCLK for the SPI interface. The SCLK can be programmed as needed. Please see **Table** 1 for an example of the memory map.

- 2. The programming for the LIU will begin when OE on the Xilinx XC18V00 goes high. Therefore, one must consider if any delay is necessary in the application. Generally, connecting the OE pin to a powerup delay device is sufficient.

Figure 2. SPI-to-LIU connection diagram.

**Table 1. Memory Configuration**

| Table 1. W | D7  | D6   | D5  |                                   | D3           | D2      | D1       | D0     |

|------------|-----|------|-----|-----------------------------------|--------------|---------|----------|--------|

| Address    | CSB | SCLK | SDI | X                                 | X            | X       | X        | X      |

| 0x00       | 1   | 0    | 0   | Start o                           | of Write     | e Cycle | <b>)</b> |        |

| 0x01       | 0   | 0    | 0   | •                                 |              | \       |          |        |

| 0x02       | 0   | 1    | 0   | Bit A0 (Always a "0" for a write) |              |         |          | write) |

| 0x03       | 0   | 0    | 1   | Bit A1                            |              |         |          |        |

| 0x04       | 0   | 1    | 1   |                                   |              |         |          |        |

| 0x05       | 0   | 0    | 0   | D:4 A O                           |              |         |          |        |

| 0x06       | 0   | 1    | 0   | Bit A2                            |              |         |          |        |

| 0x07       | 0   | 0    | 0   | D:4 A O                           |              |         |          |        |

| 80x0       | 0   | 1    | 0   | DIL AS                            | Bit A3       |         |          |        |

| 0x09       | 0   | 0    | 0   | Bit A4                            | D:+ A 4      |         |          |        |

| 0x0A       | 0   | 1    | 0   | DIL A4                            | DIL A4       |         |          |        |

| 0x0B       | 0   | 0    | 0   | Bit A5                            |              |         |          |        |

| 0x0C       | 0   | 1    | 0   |                                   |              |         |          |        |

| 0x0D       | 0   | 0    | 0   | Bit A6                            |              |         |          |        |

| 0x0E       | 0   | 1    | 0   | DIL AU                            |              |         |          |        |

| 0x0F       | 0   | 0    | 0   | Bit A7                            | Rit Δ7       |         |          |        |

| 0x10       | 0   | 1    | 0   | Dit / (/                          |              |         |          |        |

| 0x11       | 0   | 0    | 0   | Bit D0                            | Bit D0 (LSB) |         |          |        |

| 0x12       | 0   | 1    | 0   |                                   |              |         |          |        |

| 0x13       | 0   | 0    | 1   | Bit D1                            |              |         |          |        |

| 0x14       | 0   | 1    | 1   |                                   |              |         |          |        |

| 0x15       | 0   | 0    | 1   | Bit D2                            |              |         |          |        |

| 0x16       | 0   | 1    | 1   |                                   |              |         |          |        |

| 0x17       | 0   | 0    | 0   | Bit D3                            | Bit D3       |         |          |        |

| 0x18       | 0   | 1    | 0   |                                   |              |         |          |        |

| 0x19       | 0   | 0    | 0   | Bit D4                            | Bit D4       |         |          |        |

| 0x1A       | 0   | 1    | 0   |                                   |              |         |          |        |

| 0x1B       | 0   | 0    | 1   | Bit D5                            | Bit D5       |         |          |        |

| 0x1C       | 0   | 1    | 1   |                                   |              |         |          |        |

| 0x1D       | 0   | 0    | 1   | Bit D6                            |              |         |          |        |

| 0x1E | 0 | 1 | 1 |                    |  |

|------|---|---|---|--------------------|--|

| 0x1F | 0 | 0 | 0 | Bit D7             |  |

| 0x20 | 0 | 1 | 0 | DIL D1             |  |

| 0x21 | 1 | 0 | Χ | End of Write Cycle |  |

| 0x22 | 1 | Χ | Χ | End of Write Cycle |  |

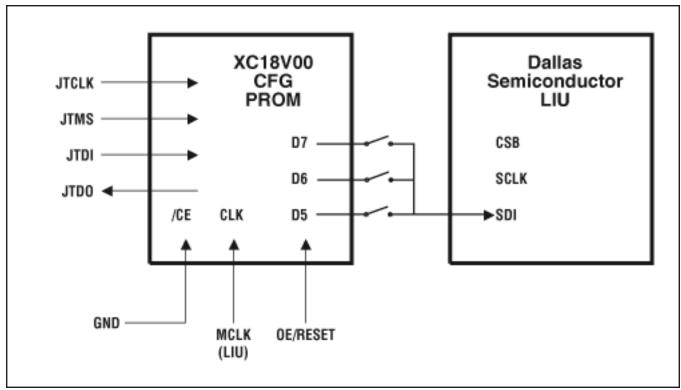

Configuring LIU(s) for Other Operations By connecting the D5, D6, and D7 pins of the Xilinx XC18V00 device through a switch to the LIU's SDI pin, different loopback configurations can be implemented.

Figure 3. Diagram of an SPI connection which enables loopback.

### Conclusion

The Dallas Semiconductor Line Interface Units (LIUs) have different modes of operation that can be implemented without a microcontroller, but instead by using configurable PROM like the Xilinx XC18V00 device family. Modifications to the LIUs should be made based on the customer's needs.

If you have questions about any Dallas Semiconductor telecom products, please contact the Telecom Products applications support team by emailing <u>telecom.support@dalsemi.com</u>, or by calling (01) 972-371-6555.

#### **More Information**

```

DS21348: QuickView -- Full (PDF) Data Sheet -- Free Samples

```

DS21448: QuickView -- Full (PDF) Data Sheet -- Free Samples

DS2148: QuickView -- Full (PDF) Data Sheet -- Free Samples

DS3150: QuickView -- Full (PDF) Data Sheet

DS3151: QuickView -- Full (PDF) Data Sheet -- Free Samples

DS3152: QuickView -- Full (PDF) Data Sheet

DS3153: QuickView -- Full (PDF) Data Sheet

DS3154: QuickView -- Full (PDF) Data Sheet -- Free Samples

DS3251: QuickView -- Full (PDF) Data Sheet

DS3252: QuickView -- Full (PDF) Data Sheet

DS3253: QuickView -- Full (PDF) Data Sheet

DS3254: QuickView -- Full (PDF) Data Sheet